系统集成

FPGA多速率信号处理(三)

发布人: 发布时间:2021-06-15

对于发射端来讲,基带信号需要经过多速率发送处理器处理后,再进行数/模转换(DAC)。多速率发送处理器的一般结构,主要由四部分组装成:可编程插值FIR滤波器(RCF)、两个固定系数的FIR滤波器(FFIR)、高速的CIC插值滤波器以及数控频率振荡器(NCO)。

RCF完成对输入信号的采样,采样倍数1~16,由于需要工作在高速时钟下,其阶数一般不会太高。FFIR对输入信号进行2倍采样,如果FFIR的带宽达到输入采样率的一半,则能够有效抑制带外信号的噪声。CIC滤波器一般采用2~5阶,完成对输入信号1~32倍的采样,其有效的线性相位冲激响应是由其插值率决定。NCO主要完成两件事:一是产生载波频率,二是完成数据调制的复数乘法。NCO需要高比特数的频率调谐精度,并需要抑制幅度和相位抖动来无杂散动态范围。

04多速率接收处理器设计

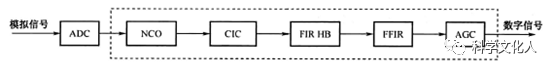

在无线通信中,多速率接收处理器在ADC之后工作,主要包含五部分:数控频率振荡器(NCO)、高速的CIC抽取滤波器、可编程抽取FIR半带滤波器(FIR HB)、两个固定系数的FIR滤波器(FFIR)、以及自动增益控制模块(AGC),其结构如图所示。

其中,NCO、CIC、FIR HB、FFIR的功能和实现与发送端类似。AGC模块主要自适应地调整信号通道增益,确保不超出模拟信号的线性范围,或保证数字信号不超出有效字长的限制,从而保证信号在一个动态范围都能工作。

RCF完成对输入信号的采样,采样倍数1~16,由于需要工作在高速时钟下,其阶数一般不会太高。FFIR对输入信号进行2倍采样,如果FFIR的带宽达到输入采样率的一半,则能够有效抑制带外信号的噪声。CIC滤波器一般采用2~5阶,完成对输入信号1~32倍的采样,其有效的线性相位冲激响应是由其插值率决定。NCO主要完成两件事:一是产生载波频率,二是完成数据调制的复数乘法。NCO需要高比特数的频率调谐精度,并需要抑制幅度和相位抖动来无杂散动态范围。

04多速率接收处理器设计

在无线通信中,多速率接收处理器在ADC之后工作,主要包含五部分:数控频率振荡器(NCO)、高速的CIC抽取滤波器、可编程抽取FIR半带滤波器(FIR HB)、两个固定系数的FIR滤波器(FFIR)、以及自动增益控制模块(AGC),其结构如图所示。

其中,NCO、CIC、FIR HB、FFIR的功能和实现与发送端类似。AGC模块主要自适应地调整信号通道增益,确保不超出模拟信号的线性范围,或保证数字信号不超出有效字长的限制,从而保证信号在一个动态范围都能工作。

在工程中,我们需要关注以下设计要点:

设计要点

抽取:下采样器+抗混叠滤波器设计

插值:抗镜像滤波器+上采样器设计

CIC滤波器设计

FIR半带滤波器设计

多相分解技术

地址:河北省秦皇岛市 电话:0335-8691689 E-mail:ddcs0335@163.com 备案号:冀ICP备19014184号-1

版权所有:秦皇岛市东伏电子 东大测试 技术支持:创想网络 您是第958222位访客 备案号:冀ICP备19014184号-1

备案号:冀ICP备19014184号-1

友情链接: 变压器变比组别测试仪 油分析仪 高清执法记录仪 煤炭检测仪器 冷媒表

版权所有:秦皇岛市东伏电子 东大测试 技术支持:创想网络 您是第958222位访客

友情链接: 变压器变比组别测试仪 油分析仪 高清执法记录仪 煤炭检测仪器 冷媒表