系统集成

FPGA多速率信号处理(一)

发布人: 发布时间:2021-06-13

一般情况下,多速率系统能够比单速率系统更为有效地处理信号,在多速率系统内部各节点,根据设计需要,进行内插和抽取,从而满足AD/DA和基带速率需求。

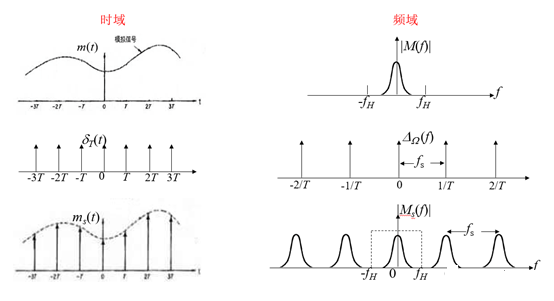

在工程中,中频采样技术使用广泛,在中频对模拟信号进行数字化,依据的是带通采样定理。我们知道,对于低通模拟信号进行抽样,遵循奈奎斯特抽样定理,也就是抽样频率fs需要大于等于模拟信号最高频率fH的2倍,才能对数字化后的信号无失真恢复出原始信号。

学习过通信原理的同学都知道,通过调制解调技术,我们可以实现频谱搬移,并实现远距离通信。从基带信号到射频信号,从理论上讲,我们可以一步到位,直接将低频的基带信号调制到射频,这样的技术叫零中频。零中频结构简单,有利于集成和降低成本,在终端获得广泛应用。当然零中频存在两个弱点:直流偏置和闪烁噪声。直流偏置因本振泄露导致,闪烁噪声则与频率有关,频率越高,闪烁噪声越小,反之越大。

在早期的实际系统中,基带信号经过两步走达到射频:先将基带调制到中频,达到几百MHz,然后再次调制,达到射频,GHz级别。接收机则采用两次降频到基带。这样的结构叫超外差结构,应用广泛。

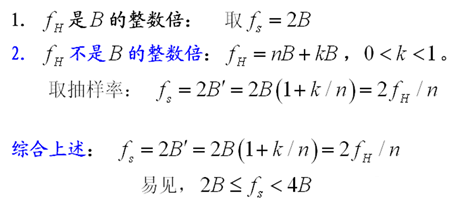

再回到带通采样。对于带通信号,其频谱位于某一频率区间,其带宽B=fH-fL,则此时的采样率fs需满足:

由于此时的采样率已超过了奈奎斯特定义的最低采样率,进而被称为过采样。过采样的好处是,可以将采样过程中固有的量化噪声均匀地分散在更大的带宽上,从而降低有效信号带宽上的噪声功率。再通过数字滤波器对带外噪声进行衰减,从而得到比临界采样信号更优的信噪比。

ADC的采样率过高,会给FPGA进行数据处理带来压力。我们一方面希望利用过采样的优点,另一方面,我们不希望FPGA处理过于复杂,于是通过降低数字信号采样率来满足基带处理需求,这就是抽取。

实际上,抽取并不难理解,我们可以与生活中的抽样调查联系起来。样本(数据)过大,统计(处理)起来就复杂。比如,让你去调查一下,成都的FPGAer的平均薪资。你可能会从招聘网站、朋友、同事等了解到相关信息,从而大概知道成都的FPGA平均薪资水平,当然不可能去把每一个FPGAer都问一遍,再做统计,于是有了抽样调查。

在利用FPGA进行信号处理时,抽取后的信号,数据率相对较低,因而能够有效降低系统对FPGA资源的占用。这就好比吃饭,你不能吃太快,送到嘴里先嚼几下再咽下去,降低吞的频率。

在一些系统中,则需要提高采样率,即为内插。将数字基带信号搬移到目标载频后,通过内插的方式得到更高的采样率,从而驱动高速DAC。为什么需要采样率高的DAC呢?这是因为DAC采样率越高,其输出端频谱图像之间的频域分离度越高,这样可以简化DAC后的模拟滤波器工作,提升信噪比。

地址:河北省秦皇岛市 电话:0335-8691689 E-mail:ddcs0335@163.com 备案号:冀ICP备19014184号-1

版权所有:秦皇岛市东伏电子 东大测试 技术支持:创想网络 您是第958214位访客 备案号:冀ICP备19014184号-1

备案号:冀ICP备19014184号-1

友情链接: 变压器变比组别测试仪 油分析仪 高清执法记录仪 煤炭检测仪器 冷媒表

版权所有:秦皇岛市东伏电子 东大测试 技术支持:创想网络 您是第958214位访客

友情链接: 变压器变比组别测试仪 油分析仪 高清执法记录仪 煤炭检测仪器 冷媒表