数据采集器核心器件-FPGA(二)

发布人: 发布时间:2021-06-11

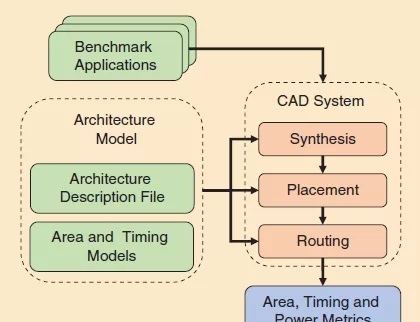

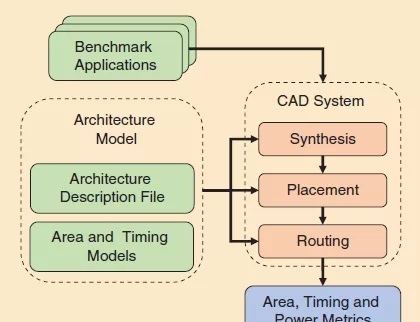

如图2所示,FPGA架构评估流程由三个主要组件组成:一套基准应用、一个架构模型和一个CAD系统。与为特定功能构建的ASIC不同,FPGA是为许多用例设计的通用平台,其中一些用例甚至可能在FPGA构建时不存在。因此,在实现代表关键FPGA市场和应用领域的各种基准设计时,将根据效率来评估FPGA架构。通常,每个FPGA供应商都有一套精心选择的基准设计,这些设计是从专有系统实现和各种客户应用中收集的。还有几个开源基准套件,如经典的MCNC20[13]、VTR[14]和Titan23[15]套件,这些在学术FPGA架构和CAD研究中是常用的。虽然早期的学术FPGA研究使用了MCNC设计套件,但这些电路现在太小(数千个逻辑原语)和太简单(只有输入输出和逻辑),无法代表现代FPGA用例。VTR,尤其是Titan套件更大、更复杂,使它们更具代表性,但随着FPGA容量和应用复杂性的不断增长,通常需要新的基准套件。图2:FPGA架构评估流程评估流程的第二部分是FPGA架构模型。FPGA的设计涉及来自架构级组织的许多不同决策(例如块的数量和类型、线段长度的分布、逻辑簇和逻辑元件的大小)到晶体管级电路实现(例如可编程开关类型、布线缓冲器晶体管大小、寄存器实现)。还涉及到不同的实现风格;逻辑块和可编程布线被设计和布局为全定制的电路,而大多数硬化的块(例如DSP)分别为模块内核和外设混合了标准单元和全定制设计。一些模块(存储、输入输出)甚至包括重要的模拟电路。所有这些不同的组件都需要仔细建模,以评估整个FPGA架构。除了从每个组件的电路级实现中获得的面积、时序和功率模型之外,这通常使用架构描述文件来获取,架构描述文件指定不同的FPGA块和布线架构的组织和类型。最后,使用可重定位的CAD系统,如VTR [14],将选定的基准应用映射到指定的FPGA架构上。这种CAD系统由一系列复杂的优化算法组成,这些算法将写在HDL中的基准综合为电路网表,将其映射到不同的FPGA块,将映射的块放置在FPGA上的特定位置,并使用指定的可编程布线架构在它们之间布线连接。然后,我们用由CAD系统产生的实现来评估几个关键指标。总面积是应用使用的FPGA块的总面积,以及其中包含的可编程布线。时序分析器找到通过块和布线的关键路径,以确定应用时钟的最大频率。功耗是根据使用的资源和信号切换速率来估计的。FPGAs从来不是为一个应用设计的,所以这些指标在所有基准中是平均的。最后,根据架构目标(例如高性能或低功率)。其他指标,如CAD工具运行时间以及CAD工具未能在一个架构上布线一些基准也经常被考虑。

备案号:冀ICP备19014184号-1

备案号:冀ICP备19014184号-1