系统集成

数据采集器核心器件-FPGA(一)

发布人: 发布时间:2021-06-10

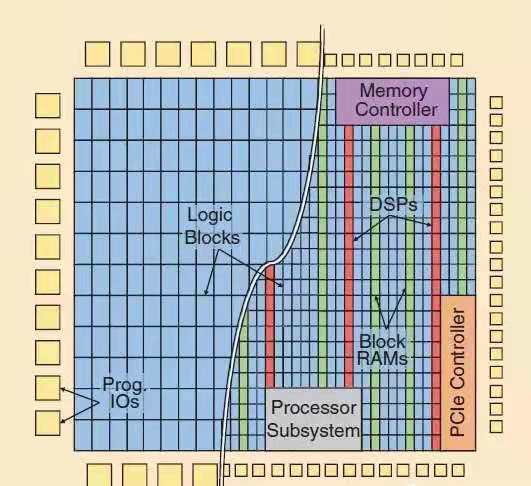

与构建定制专用集成电路(ASIC)相比,FPGAs的非重复性工程成本低得多,上市时间也短得多。预制的现成的FPGA可以用来在几周内实现一个完整的系统,跳过了定制ASIC通常要经历的物理设计、布局、制造和验证阶段。它们还允许持续的硬件升级,以支持新功能或通过在现场部署后简单地加载新比特流来修复错误,因此称为现场可编程。这使得FPGAs成为中小型设计的引人注目的解决方案,特别是在当今市场产品周期快的情况下。FPGAs的比特级可重新配置性使得能够实现每个应用所需的精确硬件(例如:数据路径位宽、流水线级、并行计算单元的数量、存储子系统等。)而不是通用处理器(CPUs)或图形处理单元(GPUs)的固定的单一尺寸结构。因此,通过实现无指令流硬件[1]或覆盖有应用定制流水线和指令集的处理器[2],它们可以实现比CPU或GPU更高的效率。

这些优势促使FPGAs在许多应用领域采用,包括无线通信、嵌入式信号处理、网络、ASIC原型、高频交易等[3]?[7]。它们最近也被大规模部署在数据中心,以加速搜索引擎、数据包处理[9]和机器学习[10]等工作负载。然而,与ASIC相比,FPGA硬件的灵活性带来了效率成本。库恩和罗斯[11]表明,仅使用FPGA的电路比相应的ASIC实现平均大35倍,慢4倍。最近的一项研究[12]表明,对于大量使用其他FPGA(如随机存取存储器和数字信号处理器)的全功能设计,这一面积差距有所缩小,但仍为9倍。FPGA设计师试图尽可能地缩小这种效率差距,同时保持可编程性,使FPGA在广泛的应用中非常有用。

地址:河北省秦皇岛市 电话:0335-8691689 E-mail:ddcs0335@163.com 备案号:冀ICP备19014184号-1

版权所有:秦皇岛市东伏电子 东大测试 技术支持:创想网络 您是第958220位访客 备案号:冀ICP备19014184号-1

备案号:冀ICP备19014184号-1

友情链接: 变压器变比组别测试仪 油分析仪 高清执法记录仪 煤炭检测仪器 冷媒表

版权所有:秦皇岛市东伏电子 东大测试 技术支持:创想网络 您是第958220位访客

友情链接: 变压器变比组别测试仪 油分析仪 高清执法记录仪 煤炭检测仪器 冷媒表